This allows many bugs to be found and fixed before simulation making simulation faster and more effective and reducing overall cost time and effort. For an undisclosed amount.

The Cadence Verification Suite of tools accelerates system design IP and SoC verification and bring-up adding faster project execution with the Xcelium Parallel Simulator and the Protium S1 FPGA-Based Prototyping Platform.

Formal verification tools cadence. The Cadence Verification Suite of tools accelerates system design IP and SoC verification and bring-up adding faster project execution with the Xcelium Parallel Simulator and the Protium S1 FPGA-Based Prototyping Platform. The Cadence JasperGold Formal Property Verification FPV App fully validates block-level properties and high-level requirements. It enables exhaustive and complete verification and provides rapid bug detection as well as end-to-end full proofs of expected design behavior.

This command invokes the Cadence Encounter Conformal tool and also runs formal verification between your HDL design files and the Quartus II software-generated post-fit netlist. Observe the results in the Cadence Encounter Conformal tool. Formal verification is a well-known white-box approach where mathematical techniques are used to prove an assertion or a property of the design.

The property to be proven may be related to the chips overall functional specification or it may represent the internal design behavior. To help you create high-quality differentiated electronic products Cadence offers a broad portfolio of tools to address an array of challenges related to custom IC digital IC package and PCB design and system-level verification. Find the tools and methodologies you need to meet your power performance and area targets.

Overcome mixed-signal design constraints. Achieve faster design closure. Synopsys VC Formal VC LP VC SpyGlass and SpyGlass tools enable designers and verification engineers to quickly analyze and check RTL designs very early in the design flow with no need for complex setup testbenches or stimulus.

This allows many bugs to be found and fixed before simulation making simulation faster and more effective and reducing overall cost time and effort. JasperGold is a formal verification tool initially introduced in 2003. In 2019 Cadence announced new machine learning technology to automate JasperGold solver selection and parameterization to achieve faster first-time proofs.

Additionally to optimize regression runs. Formal verification is the overarching term for a collection of techniques that use static analysis based on mathematical transformations to determine the correctness of hardware or software behavior in contrast to dynamic verification techniques such as simulation. Cadence buys formal tool vendor Verplex.

By Michael Santarini 07142003 0. In the latest move between the EDA industrys top rivals Cadence Design Systems Inc. Said it has acquired privately held formal verification tool vendor Verplex Inc.

For an undisclosed amount. The acquisition which was expected will bring to Cadence 104 new employees Verplexs BlackTie assertion based verification system and Verplexs stalwart Conformal line of equivalence checkers plus to Cadence. We chose 3 configurations to run on.

First the Cadence network using 12 cores representative of the resources available to formal verification engineers in many mid-size JasperGold customers. Second the Cadence network extended with AWS using Amazon EC2 instances to provide 96 cores. And the third configuration with 960 cores.

The Quartus II software provides formal verification support for Altera designs through interfaces with a formal verification EDA tool the Cadence Encounter Conformal software. Use the Encounter Conformal software to verify the functional equivalence of a post-synthesis Verilog Quartus Mapping vqm netlist file from Synopsys Synplify. Each property can be used by a Formal Verification tool such as Cadences Incisive Formal Verifier as an assertion check or an assumption environment constraint.

Most of the time assumptions are applied to the DUTs inputs and assertions to the DUTs outputs. Cadence Encounter Conformal Support The QuartusII software provides formal verification support for Alteradesigns through interfaces with a formal verification EDA tool the Cadence Encounter Conformal Logic Equivalence Check LEC software. The two types of formal verification are equivalence checking and model checking.

Formal ABV Tool. Mentor Questa FV Calypto. Manual automatic selection.

10 formal engines Manual automatic selection. 15-20 formal engines Manual automatic selection. All you need is a decent formal verification tool your RISC-V RTL in VerilogVHDLSystemVerilog and a coverage specification if you are interested in our coverage analysis.

Currently we support tools from Cadence Design Systems Mentor and Synopsys. You will need to read fill out and agree to the Cadence EULA before you can utilize any Cadence software. Cadence Cadence has been talking about safety critical in a general fashion since 2014 including presenting on it at different conferences.

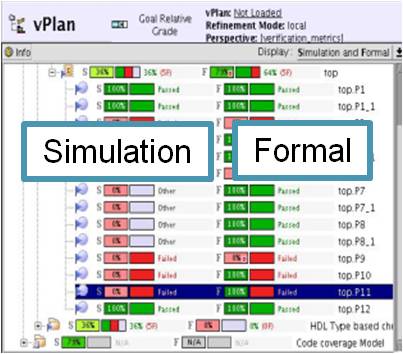

They support systematic verification with both the RTL simulation Incisive and formal Jasper verification tools.